Alors que la miniaturisation de l’électronique traditionnelle à base de silicium approche de ses limites physiques, l’industrie des semi-conducteurs fait face à des défis croissants : inefficacité énergétique, goulots d’étranglement dans les architectures de type von Neumann, et une rigidité du matériel inadaptée aux besoins de l’intelligence artificielle. Les nouvelles applications — telles que les systèmes autonomes, l’Internet des objets (IoT) et l’apprentissage en temps réel — exigent un changement radical dans l’intégration du calcul et de la mémoire à l’échelle nanométrique.

Développée par un consortium international de premier plan, comprenant l’Université de Strasbourg, l’Institut des Nanotechnologies de Lyon, l’Université Paris-Saclay et le National Institute for Materials Science (Japon), nous avons le plaisir de présenter une avancée majeure en nanoélectronique : le transistor à effet de champ à grille flottante inversée Van der Waals (IFGFET) — une nouvelle topologie de dispositif qui combine logique, mémoire et calcul neuromorphique dans une seule architecture.

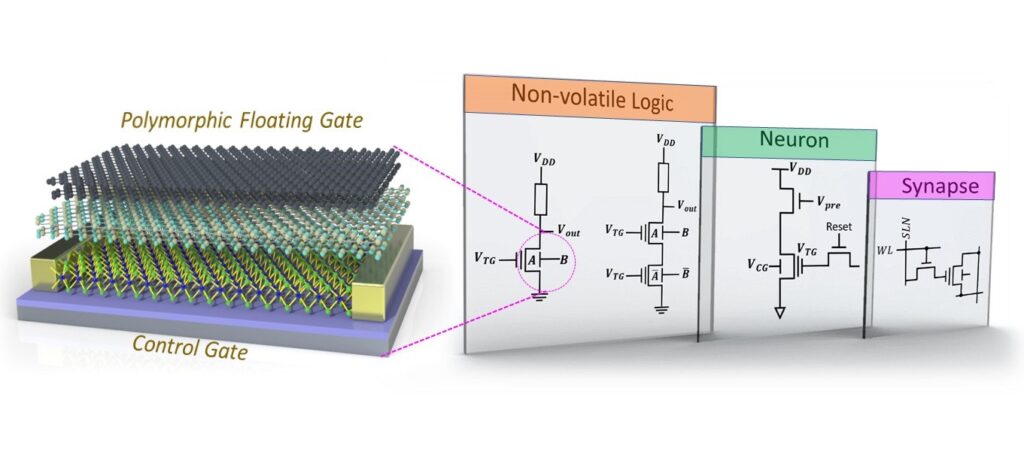

Cette innovation repose sur des hétérostructures Van der Waals, combinant des semi-conducteurs ReS₂ avec une (top) grille flottantes polymorphique and une (bottom) grille de control. Cette topologie permet l’accès direct à la grille flottante et améliore considérablement le contrôle électrostatique du canal.

En outre, cette technologie offre des caractéristiques révolutionnaires telles que :

- Fonctionnalité double mode : fonctionne à la fois comme porte logique reconfigurable et comme mémoire non-volatile.

- Capacités neuromorphiques : émule le comportement synaptique avec une précision de 92 % dans des réseaux de neurones artificiels, et prend en charge des circuits de neurones impulsionnels.

- Conception compacte et sécurisée : permet la création de circuits IA programmables à la demande avec une sécurité intrinsèque grâce à une mémoire auto-effaçable.

- Contrôle électrostatique optimisé : la topologie inversée améliore les performances par rapport aux FGFETs conventionnels grâce à un couplage grille–canal renforcé.

Ce dispositif reconfigurable pourrait ouvrir la voie à de nouveaux horizons en calcul en mémoire, calcul neuromorphique, réseau à spike et matériel IA sécurisé.

👉 Retrouvez l’article complet dans ACS Nano: Lien vers l’article

Contact : dayen@unistra.fr